As a part of the Digital electronics Lab End -Semester project , I implemented a basic Arithmetic and Logical Unit (ALU) in a group of two students . Following was our problem Statement - "To design a 4 function ALU to execute the following operations - add , multiply , AND and OR . The operands are 8 bits defined as a[7:0] and b[7:0] . The result of all operations should be 16 bits . Also , implement the following flags -

1)Parity Flag(pf)- pf=1 if the result has even number of 1s , else pf=0

2)Sign flag(sf)- sf reperents the state of leftmost result bit

3)Zero flag(zf) - zf=1 if the result of an operation is zero , else zf=0

"

Following is the code to implement the above problem statement . All coding and analysis was done in Xilinx FPGA programming Software -

1)Parity Flag(pf)- pf=1 if the result has even number of 1s , else pf=0

2)Sign flag(sf)- sf reperents the state of leftmost result bit

3)Zero flag(zf) - zf=1 if the result of an operation is zero , else zf=0

"

Following is the code to implement the above problem statement . All coding and analysis was done in Xilinx FPGA programming Software -

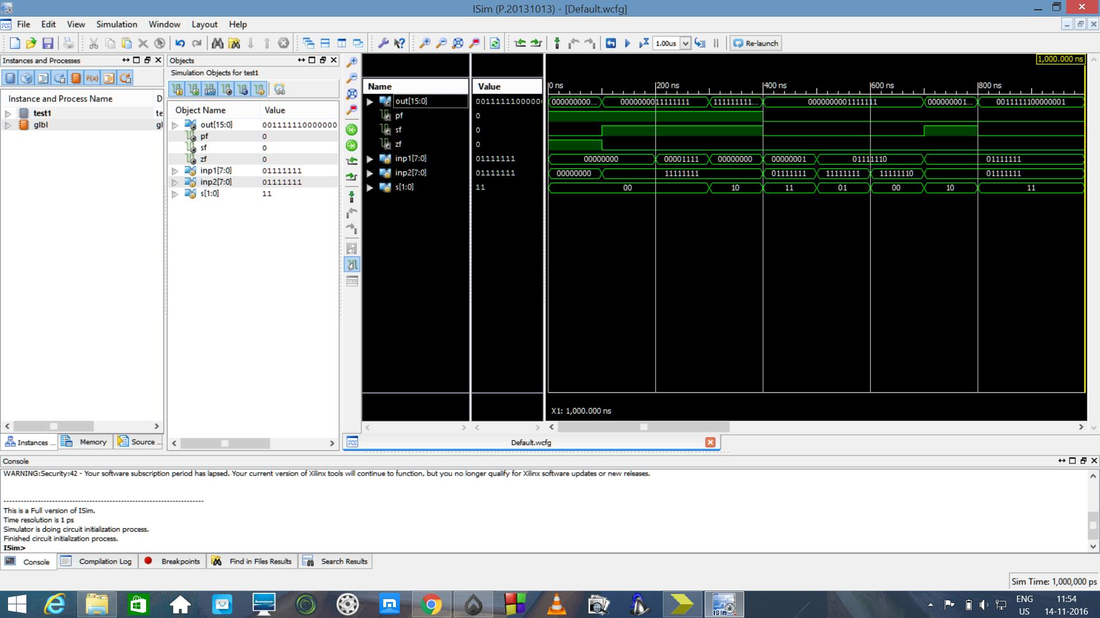

Following is a snapshot of the testbench result -